|

|

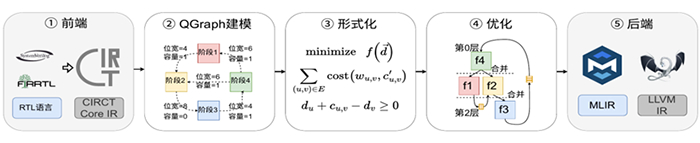

图 Khronos芯片仿真架构

在国家自然科学基金项目(批准号:T2293700、T2293701)等资助下,北京大学集成电路学院黄如院士与梁云教授团队近期提出了高效的芯片仿真EDA技术。针对通用处理器、密码学、流式压缩、深度学习等多种架构的芯片设计,相比于目前最快的开源芯片仿真器Verilator,该技术能够将芯片仿真速度平均加速2倍,最高加速4.3倍。论文以《Khronos:融合内存访问的RTL仿真》(Khronos: Fusing Memory Access for Improved RTL Simulation)为标题,于2023年10月28日发表在《芯片微架构国际研讨会》(International Symposium on Microarchitecture,简称MICRO)上。论文链接:https://doi.org/10.1145/3613424.3614301。

芯片仿真是芯片设计与验证中不可或缺的一个环节,同时也是最耗时的一个环节。芯片仿真主要借助EDA工具,通过计算机结合测试激励来模拟芯片在真实环境下的运行状况,帮助工程师通过各种调试手段来判断运行结果是否符合预期。根据统计,芯片设计与验证的70%的时间用在仿真和验证。芯片仿真中的一个重要步骤是寄存器传输级(RTL)仿真。在RTL仿真中,软件RTL仿真器因为其灵活性高和调试能力强,在RTL仿真中有重要的地位。然而,软件RTL仿真速度慢,需要消耗大量时间。广泛使用的软件RTL仿真器主要来自美国的EDA公司包括新思(Synopsys)的VCS,英特尔(Intel)的ModelSim和开源的Verilator等。针对工业级的大规模设计,软件RTL仿真往往需要几天甚至几周的时间,严重制约了芯片开发的流程。因此,面对芯片开发时间长的问题,加快RTL仿真的速度非常重要。

针对这一难题,该研究团队开创性地提出了跨时钟周期的RTL仿真方法,能够大幅减小RTL仿真迭代中的内存数据传输。之前针对RTL仿真的加速主要是通过图分割并行或延迟求值(lazy evaluation)等方法。虽然这些优化方法在加速仿真上有效,但优化能力局限在了一个周期内。该研究团队通过分析RTL的时钟边缘数据依赖,将RTL仿真建模为整数线性约束下的非线性优化问题,通过数学建模和求解实现跨周期的仿真优化与加速。这样的优化能显著提升仿真过程中的指令吞吐量,减小仿真需要的指令总数。通过跨时钟优化,减少42%的寄存器状态和38%的内存访问,实现平均2.0倍(最高4.3倍)的仿真加速。

目前,该仿真器已经开源,开源链接:https://github.com/pku-liang/ksim。接下来,团队将继续优化性能,同时将技术推广到中国的EDA产业和开源社区。