| |

|

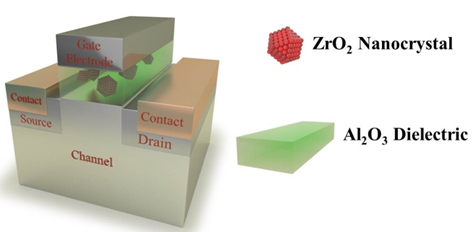

图. 纳米晶(Nanocrystal-Embedded-Insulator,NEI)铁电晶体管示意图

在国家自然科学基金项目(批准号:61534004,61604112,61622405,61874081)资助下,西安电子科技大学韩根全、郝跃等在铁电场效应晶体管研究领域取得突破性进展,发明了新型纳米晶铁电材料(Nanocrystal-Embedded-Insulator,NEI)并制备了铁电负电容晶体管器件。研究成果以“Nanocrystal-Embedded-Insulator Ferroelectric Negative Capacitance FETs with Sub-kT/q Swing”(陡峭亚阈值摆幅纳米晶铁电负电容场效应晶体管)为题,于2019年1月作为封面文章发表在微电子器件领域旗舰期刊IEEE Electron Device Letters(《IEEE电子器件快报》)上。论文链接:https://ieeexplore.ieee.org/document/8537985。

利用铁电材料作为栅介质制备的铁电晶体管是有望突破传统MOSFET器件玻尔兹曼限制的新型信息器件之一,在低功耗电路和非易失存储等方面有广泛应用前景。2011年德国研究人员在掺杂氧化铪(HfO2)材料中观测到铁电性,和传统铁电材料(如PZT,SBT等)相比,HfO2基铁电和CMOS工艺完全兼容,因此HfO2基铁电晶体管很快引起了微电子研究人员的极大关注。然而,从目前研究看,HfO2基铁电材料尚存在以下问题:1)掺杂HfO2的本征缺陷导致铁电材料存在不可避免的唤醒效应、印刻效应和易极化疲劳;2)实验研究显示HfO2基铁电晶体管用作非易失存储器时栅介质厚度一般为8~10 纳米,而用作负电容晶体管时栅介质厚度为4纳米左右,这限制了HfO2基铁电晶体管在集成电路先进技术节点的应用。

针对上述问题,研究团队采用先进的原子层沉积(ALD)工艺,在非晶顺电介质Al2O3中嵌入少量氧化锆(ZrO2)纳米晶颗粒,实现了新型的纳米晶铁电薄膜。该材料的铁电参数不仅可以通过改变ZrO2含量来大范围调整,而且通过使用更致密的Al2O3和ZrO2代替HfO2,有效克服了掺杂HfO2本征缺陷引起的唤醒效应、印刻效应和极化疲劳,从而提高了器件的耐久和保持特性。此外,由于NEI介质整体为不定形(amorphous)相,可以被制备得非常薄。在对NEI进行详细铁电特性表征的基础上,研究团队还制备了3.6 纳米NEI 铁电负电容器件。器件测试结果表明:和HfO2基铁电器件相比,基于该新型纳米晶铁电材料的铁电晶体管可在栅介质厚度更薄的情况下实现稳定的负电容效应,且晶体管亚阈值摆幅突破了60mV/decade物理极限。论文工作为实现3~5纳米负电容FinFET奠定了材料基础,也为我国“后摩尔时代”新器件研发提供了具有自主知识产权的技术方案。